- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTCV146PVG (IDT, Integrated Device Technology Inc)IC FLEXPC CLK PROGR P4 56-SSOP

COMMERCIALTEMPERATURERANGE

IDTCV146

PROGRAMMABLEFLEXPC CLOCKFORP4PROCESSOR

1

APRIL 2005

IDTCV146

COMMERCIAL TEMPERATURE RANGE

PROGRAMMABLE FLEXPC

CLOCK FOR P4 PROCESSOR

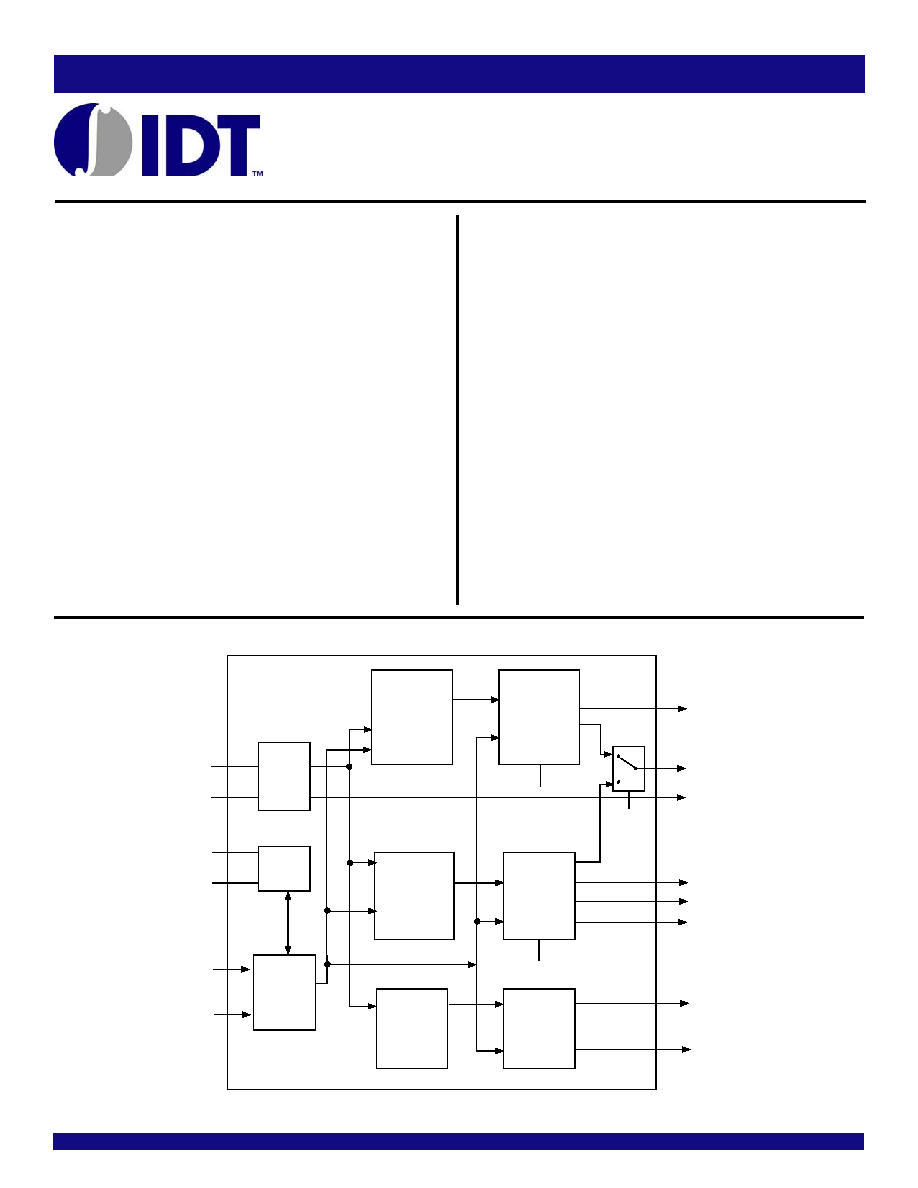

XTAL

Osc Amp

SM Bus

Controller

Control

Logic

CPU CLK

Output Buffers

Stop Logic

XTAL_IN

XTAL_OUT

SDATA

SCLK

VTT_PWRGD#/PD

FSA.B.C

IREF

CPU[1:0]

REF[1:0]

CPU_ITP/SRC6

PLL1

SSC

N Programmable

ITP_EN

SRC CLK

Output Buffer

Stop Logic

48MHz/96MHz

Output BUffer

IREF

SRC[5:0]

48MHz

DOT96

PLL2

SSC

N Programmable

PLL3

PCI[5:0], PCIF[1:0]

SATA_SRC

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2005 Integrated Device Technology, Inc.

DSC-6749/4

FEATURES:

One high precision PLL for CPU, with SSC and N program-

mable

One high precision PLL for SRC/PCI/SATA, SSC and N pro-

grammable

One high precision PLL for 96MHz/48MHz

Band-gap circuit for differential outputs

Supports spread spectrum modulation, down spread 0.5%

Supports SMBus block read/write, index read/write

Selectable output strength for REF

Allows for CPU frequency to change to a higher frequency for

maximum system computing power

Enhanced capacitance on XTAL_IN and XTAL_OUT pins

Available in SSOP package

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION:

IDTCV146 is a 56 pin clock device. The CPU output buffer is designed to

support up to 400MHz processor. This chip has three PLLs inside for CPU/

SRC/PCI, SATA, and 48MHz/DOT96 IO clocks. One dedicated PLL for Serial

ATA clock provides high accuracy frequency. This device also implements

Band-gap referenced IREF to reduce the impact of VDD variation on differential

outputs, which can provide more robust system performance.

Each CPU/SRC/PCI, SATA clock has its own Spread Spectrum selection,

which allows for isolated changes instead of affecting other clock groups.

OUTPUTS:

2*0.7V current –mode differential CPU CLK pair

6*0.7V current –mode differential SRC CLK pair, one

SATA_SRC pair

One CPU_ITP/SRC selectable CLK pair

6*PCI, two free running, 33.3MHz

1*96MHz, 1*48MHz

2*REF

KEY SPECIFICATIONS:

CPU/SRC CLK cycle to cycle jitter < 85ps

SATA CLK cycle to cycle jitter < 85ps

PCI CLK cycle to cycle jitter < 250ps

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCV149PAG

IC FLEXPC CLK PROGR K8 56-TSSOP

IDTNW6005ASG

IC CALLER ID DECODER 20SOIC

IDTNW6006AS

IC CALLER ID DECODER 20-SOIC

IDTSSTE32882HLBBKG

IC REGISTERING CLK DRIVER 176BGA

IDTSSTE32882KA1AKG

IC REGISTERING CLK DRIVER 176BGA

ISD1750SYR

IC VOICE REC/PLAY 50SEC 28-SOIC

ISD5008EYI

IC VOICE REC/PLAY 4-8MIN 28-TSOP

ISL12008IB8Z

IC RTC I2C LO-POWER 8-SOIC

相关代理商/技术参数

IDTCV146PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV149PA

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PA8

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PAG

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PAG8

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV152

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

IDTCV152PVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV152PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT